|

3059| 4

|

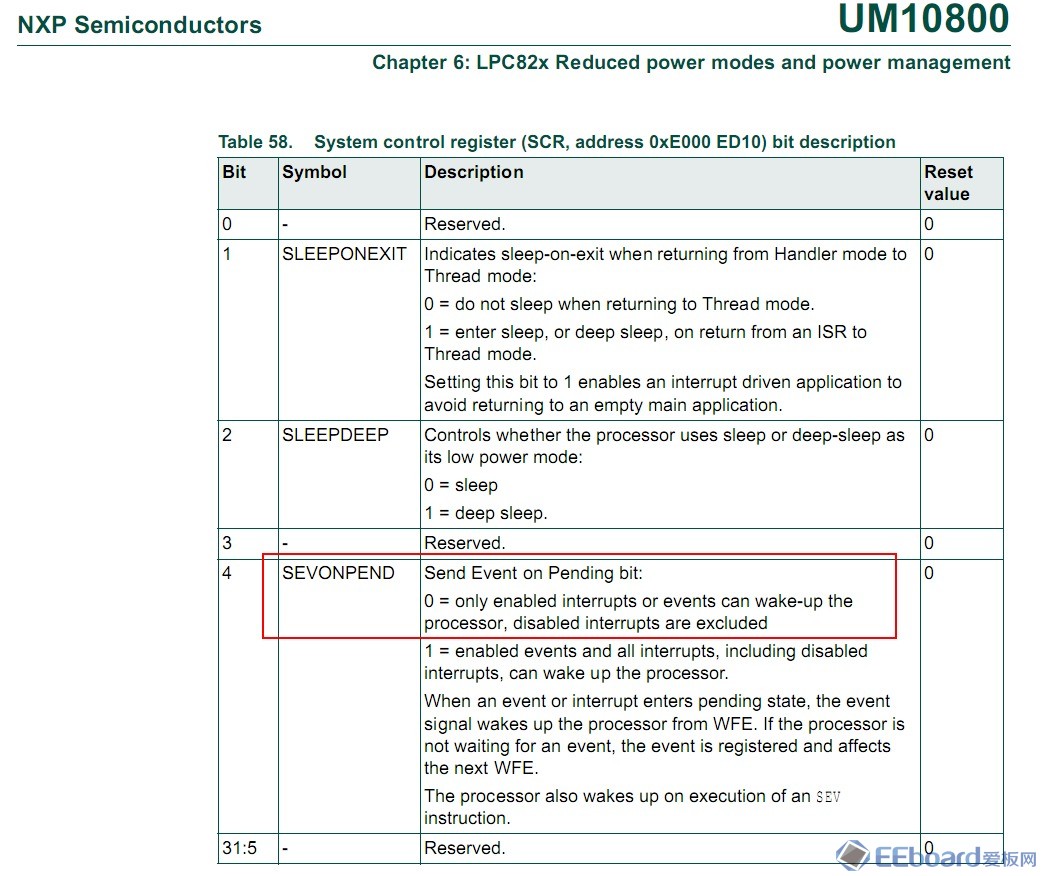

LPC824掉电模式的寄存器配置是什么意思? (SYST_CSR, 0xE000 E010 |

| ||

| ||

| ||

|

| |

关闭

站长推荐

站长推荐 /2

/2

ICP经营许可证 苏B2-20140176 苏ICP备14012660号-2 苏州灵动帧格网络科技有限公司 版权所有.

Powered by Discuz! X3.4

Copyright © 2001-2020, Tencent Cloud.

发表于 2017-1-18 11:36:35

发表于 2017-1-18 11:36:35

楼主

楼主