TA的每日心情 | 怒

2018-11-20 13:41 |

|---|

签到天数: 3 天 连续签到: 1 天 [LV.2]偶尔看看I

|

做个假设:需要将100M时钟下的脉冲同步到1M的时钟域下,如果按照打拍的方式,需要延展100拍后再进行跨时钟域才能保证信号能在1M时钟域正确采到,这种设计方法未免太愚蠢而又浪费资源。

本篇介绍两种可以同时处理快到慢、慢到快所有时钟频率的脉冲同步设计电路情况。

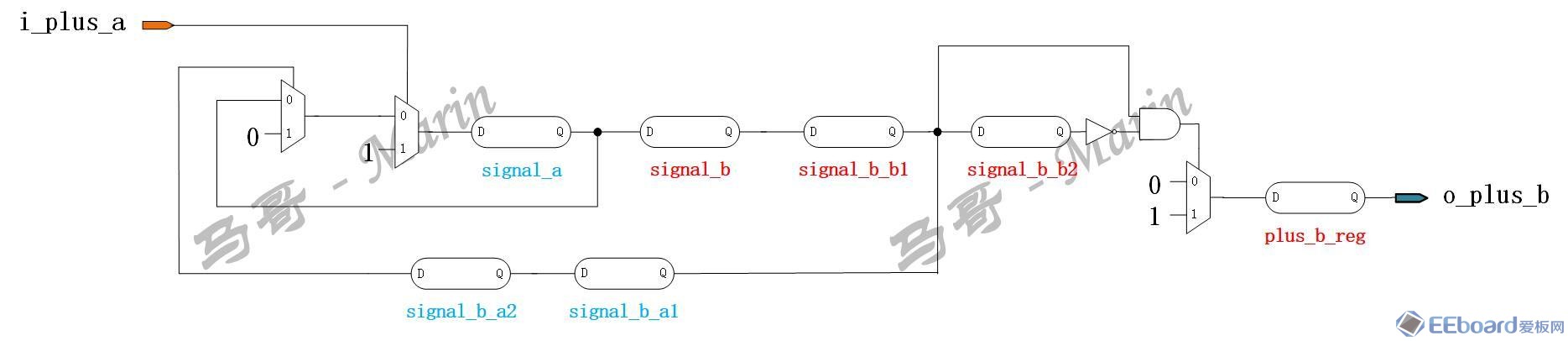

脉冲同步

注:

* 蓝色为 A 时钟域的寄存器;

* 红色为 B 时钟域的寄存器;

实现说明

该模块关键寄存器是signal_a,在A时钟域下,捕获到i_plus_a的脉冲,转化为电平反转传输到B时钟域,等待B时钟域捕获到有电平变化,signal_a再清0,等待下一个脉冲输入。

HDL代码

- module sync_pulse

- (

- //A clock domain

- input clk_A ,

- input rst_n_A ,

- //B clock domain

- input clk_B ,

- input rst_n_B ,

- //input plus(A)

- input i_puls_a ,

- //output plus(B)

- output reg o_puls_b

- );

- //------------------------------ Reg & Wire --------------------------

- reg signal_a ; // A clock domain

- reg signal_b1_a1 ; // A clock domain

- reg signal_b1_a2 ; // A clock domain

- reg signal_b ; // B clock domain

- reg signal_b_b1 ; // B clock domain

- reg signal_b_b2 ; // B clock domain

- //-------------------------------- logic -----------------------------

- always @(posedge clk_A or negedge rst_n_A)

- begin

- if(!rst_n_A)

- signal_a <= 1'b0;

- else if(i_puls_a == 1'b1)

- signal_a <= 1'b1;

- else if(signal_b1_a2 == 1'b1)

- signal_a <= 1'b0;

- end

-

-

- always @(posedge clk_B)

- begin

- signal_b <= signal_a ;

- signal_b_b1 <= signal_b ;

- signal_b_b2 <= signal_b_b1 ;

- end

-

-

- always @(posedge clk_A)

- begin

- signal_b1_a1 <= signal_b_b1 ;

- signal_b1_a2 <= signal_b1_a1;

- end

-

-

- always @(posedge clk_B or negedge rst_n_B)

- begin

- if(!rst_n_B)

- o_puls_b <= 1'b0;

- else if(signal_b_b1 && !signal_b_b2)

- o_puls_b <= 1'b1;

- else

- o_puls_b <= 1'b0;

- end

- endmodule

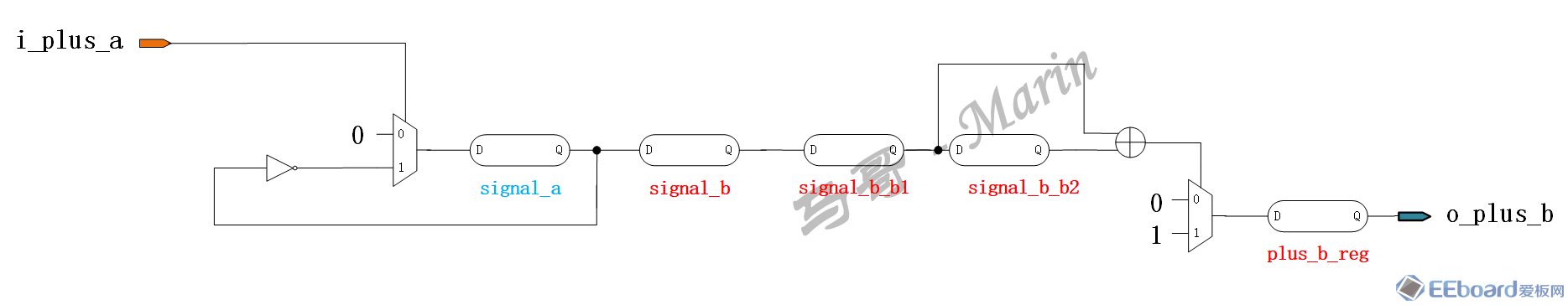

电平同步

以上的思想是脉冲跨时钟域,其实也可以通过电平跳转的方法跨时钟域:

在A时钟域检测脉冲上升沿,然后通过改变电平Z状态的方式传送给B时钟域,然后通过检测电平Z状态是否发生变化来判断A时钟域是否有脉冲。

电平同步比脉冲同步更节省资源,电路更加简单,效果也不比脉冲同步差。

本文作者:马哥 - Marin

来源:简书

|

|

/1

/1

/1

/1