本帖最后由 一蓑烟雨zsy 于 2015-11-19 14:27 编辑

近期准备抽空准备做一个Verilog HDL 的简单分享,以供初学者了解学习,技术认知有限,有错误处欢迎大家指出来一起交流。file:///C:\Users\ADMINI~1\AppData\Local\Temp\msohtmlclip1\01\clip_image001.gif 一、Verilog 语言简介

1.硬件描述语言说明

概念:硬件描述语言(HardwareDiscription Language, HDL)以文本形式来描述数字系统硬件结构和行为,是一种用形式化方法来描述数字电路和系统的语言,可以从上层到下层逐渐描述自己的设计思想,即用一系列分层次的模块来表示复杂的数字系统,并逐层进行验证仿真,再把具体的模块组合由综合工具转化成门级网络表,然后再利用布局布线工具把网络表转化为具体电路结构的实现。 优势:文本形式描述,有利于将系统划分子模块化,便于团队开发,通用性和可移植性强。

2.Veriolg VS VHDL

3.Verilog HDL 与C语言 Verilog 语言从C语言发展而来,因此具备了C语言简洁、易用的特点。主要差别体现在以下三点: 1)互连:在硬件系统中,互连是一个非常重要的组成部分,而在C语言中,并没有直接可以用于表示模块间互连的变量;而Verilog HDL 中的wire型变量配合一些驱动结构,能有效的描述出网线的互连。 2)并发:C语言天生是串行的,不能描述硬件之间的并发特性。C语言编译后,其机器指令在CPU的高速缓冲队列中基本是顺序执行的;而Verilog可以有效描述并行的硬件系统。 3)时间:运行C程序时,没有一个严格的时间概念,程序运行时间的长短主要取决于处理器本身的性能;而Verilog语言本身定义了绝对和相对的时间度量,在仿真时可以通过时间度量与周期关系描述信号之间的时间关系。

4.Verilog HDL 可以用来做什么? 1)基本逻辑门电路的实现; 2)可以用户自定义原语(UDP),既可以是组合逻辑原语,也可以是时序逻辑原语; 3)开关级基本结构模型(如pmos和nmos等) 4)提供显示语言结构指定设计中的端口到端口延时以及路径延时,以及设计的时序检查 5)支持3种方式或混合方式建模:行为描述方式(使用过程化结构建模)、数据流方式(使用连续赋值语句方式建模)和结构化方式(使用门和模块实例语句描述建模)。 6)两种数据类型:线网数据类型和寄存器数据类型。线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。 7)能够描述层次设计,可使用模块实例结构描述任何层次。 8)能够在多个层次上加以描述,从开关级、门级、寄存器传送级(RTL)到算法级,包括进程和队列级 。。。。。。

太多了,数不胜数

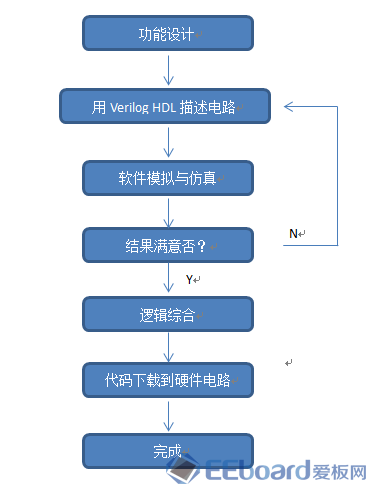

二、Verilog HDL 设计流程 典型的FPGA/CPLD 设计流程如下

三、Verilog HDL 模块设计

1. 概念: 用于描述某个设计的功能或结构及其与其他模块通信的外部端口。

模块对应着的硬件电路,他们之间是并行运行的,也是分层的,高层模块通过调用、链接底层模块的实例来实现复杂的功能。如果要将所有的功能模块连接成一个完整的系统,则需要一个模块将所有的子模块连接起来,这一模块也被称为顶层模块(Top Module )。为了便于管理,一般一个.v 文件实现一个模块

2. 模块的基本结构一个完整的Verilog HDL 模块结构如下所述:

modulemodule_name(port_list) // 模块开始

// 声明各种变量、信号

reg // 寄存器

wire // 网线

parameter // 参数

input // 输入信号

output // 输出信号

inout // 输入输出信号

function // 函数

task // 任务

// 程序代码

initial assignment

always assignment

module assignment

gate assignment

UDP assignment

continuous assignment

endmodule // 模块结束

实际中不需要具备以上所有结构特征,基本模块结构如下,可以满足一般模块设计

module < 模块名> (< 端口列表> )

< 定义>

< 模块条目>

endmodule

其中,< 模块名> 是模块唯一性的标识符;

< 端口列表> 定义了和其余模块进行通信链接的信号,根据数据流方向可以分为输入、输出和双向端口3 类;

< 定义> 用于指定数据对象为寄存器型、存储器型、网线型及过程块;

< 模块条目> 可以是initial 结构、always 结构、连续赋值或模块实例。

3. 端口说明模块端口是指模块与外界交互信息的接口,包括如下三种类型:

input: 输入接口,模块从外界读取数据的接口,在模块内不可写。

output: 输出接口,模块往外界送出数据的接口,在模块内不可读。

inout: 输入/ 输出端口,也称为双向端口,可读取数据也可送出数据,双向流动。

上述3 类端口中,input 端口只能是wire 数据类型;output 端口即可是wirel 类型,也可为reg 类型;inout 只能申明为wire 类型。

关于wire 和reg 两种类型的区别这里就不详细讨论了,可以参考下面两个链接:http://blog.chinaunix.net/uid-21227800-id-65935.html

http://wenku.baidu.com/link?url= ... 55QN_-xNChR-MRQrAMW

今天的分享就到这里了,下次继续,敬请期待。

|  /2

/2

/2

/2