TA的每日心情 | 开心

2016-9-21 20:33 |

|---|

签到天数: 29 天 连续签到: 1 天 [LV.4]偶尔看看III

|

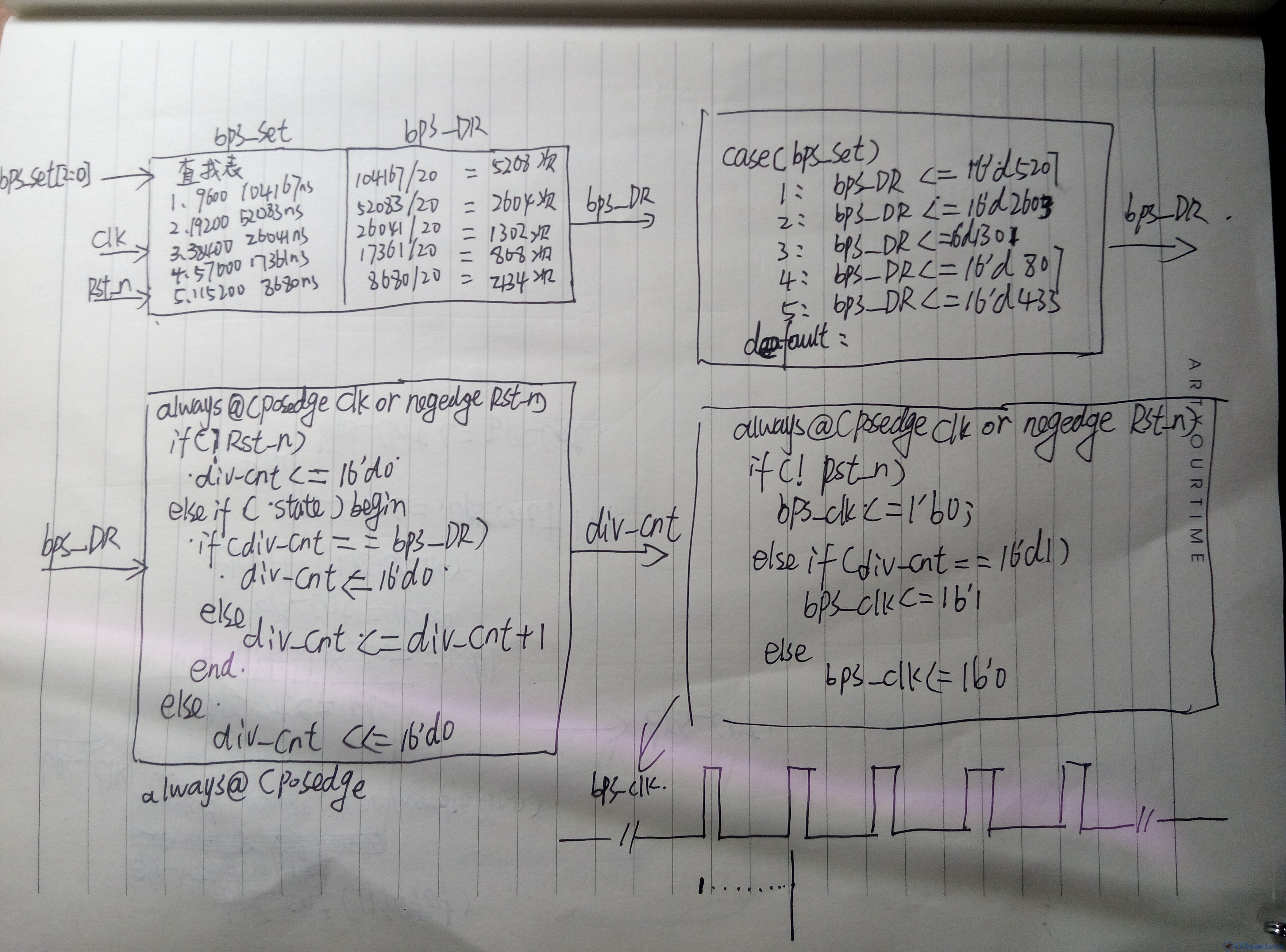

先记录一下,每天一点一点琢磨,学fpga也就半个月左右,看了一学期夏宇闻的书,现在留在学校学FPGA想做一个FPAG+STM32F7的示波器,希望大家多多指教。

继续完成我的UART_TX模块的代码编写(每天一点一点琢磨把我学明白的记录下来)

我是根据UART模型一个一个模块来代码实现

代码:- module uart_tx(Clk,Rst_n,data,bps_set,send_en,TX);

-

- input Clk;//系统时钟

- input Rst_n;//复位

- input [7:0]data;//要发送的数据

-

- input [2:0]bps_set;//波特率设置

- input send_en;//发送使能

-

- output reg TX;//UART_TX

- reg uart_state;//TX口的状态

-

-

- reg bps_clk;//波特率时钟

- reg [15:0]bps_DR;//分频计数的最大值

- reg [3:0]bps_cnt; //波特率时钟计数器

-

- localparam Start = 1'b0;//开始发送数据的标志

- localparam Stop = 1'b1;//发送结束的标志

- reg [7:0] data_r;//缓存要发送的数据 以防止在发送过程中数据被修改

-

-

- //波特率设置模块通过bps_set[0:3]来选择波特率 bps_DR 其实是一个查找表

- always @(posedge Clk or negedge Rst_n )

- if(!Rst_n)

- bps_DR <= 16'd5207;//默认的波特率是9600

- else begin

- case (bps_set)

- 0: bps_DR <= 16'd5207;//9600

- 1: bps_DR <= 16'd2603;//19200

- 2: bps_DR <= 16'd1301;//38400

- 3: bps_DR <= 16'd807;//57000

- 4: bps_DR <= 16'd433;//115200

- default : bps_DR <= 16'd5207;//其他情况的波特率是9600

- endcase

- end

-

- //分频计数器 根据上面选择的波特率 也就是分频计数的最大值来实现计数的范围达到分频

- reg[15:0] div_cnt;

- always@(posedge Clk or negedge Rst_n)

- if(!Rst_n)

- div_cnt <= 16'd0;

- else if(uart_state)begin //如果有发送使能则开始计数

- if(div_cnt == bps_DR)

- div_cnt <= 16'd0;

- else

- div_cnt <= div_cnt + 1'b1;

- end

- else

- div_cnt <= 16'b0;

- //产生bps时钟 由bps_cnt 计数实现不同波特率bps_clk 就是最终实现的波特率的时钟信号

- always@(posedge Clk or negedge Rst_n)

- if(!Rst_n)

- bps_clk <= 1'b0;

- else if(div_cnt == 16'd1)//防止滞后的情况

- bps_clk <= 1'b1;

- else

- bps_clk <= 1'b0;

- //11MUX 模块

- always @(posedge Clk or negedge Rst_n)

- if(!Rst_n)

- bps_cnt <= 4'd0;

- else if(send_en)//发送使能

- uart_state <= 1'b1;

- else if(bps_cnt == 4'd11)//一个字节的数据发送完成了

- uart_state <= 1'b0;

- else

- uart_state <= uart_state ;

- //先缓存要发送的数据 防止数据在发送过程中被修改了

- always @(posedge Clk or negedge Rst_n)

- if(!Rst_n)

- data_r <= 8'd0;

- else if(send_en )

- data_r <= data;

- else

- data_r <= data_r;

- //最终数据发送的模块

- always@(posedge Clk or negedge Rst_n)

- if(!Rst_n)

- TX <= 1'b1;

- else begin

- case(bps_cnt)

- 0:TX <= 1'b1;

- 1:TX <= Start;

- 2:TX <= data[0];

- 3:TX <= data[1];

- 4:TX <= data[2];

- 5:TX <= data[3];

- 6:TX <= data[4];

- 7:TX <= data[5];

- 8:TX <= data[6];

- 9:TX <= data[7];

- 10:TX <=Stop;

- default: TX <= 1'b1;

- endcase

- end

- endmodule

|

|

/2

/2

/2

/2